# EE 330 Lecture 29

### Bipolar Processes

- Device Sizes

- Parasitic Devices

- JFET

- Thyristors

### **Thyristors**

SCR – Basic operation

### Fall 2024 Exam Schedule

Exam 1 Friday Sept 27

Exam 2 Friday October 25

Exam 3 Friday Nov 22

Final Exam Monday Dec 16 12:00 - 2:00 PM

#### Review From Previous Lecture

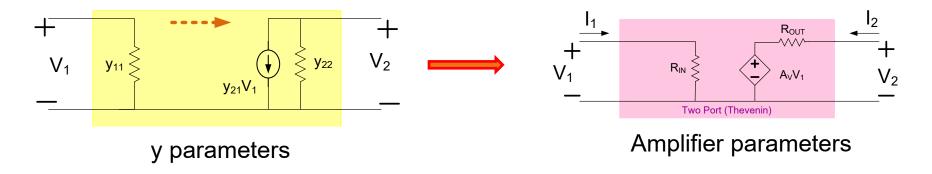

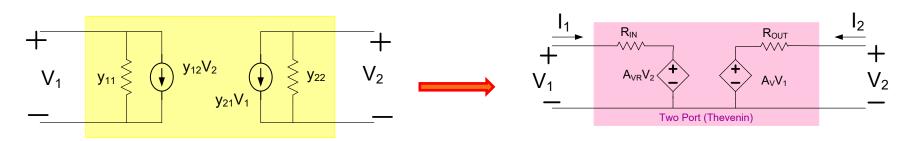

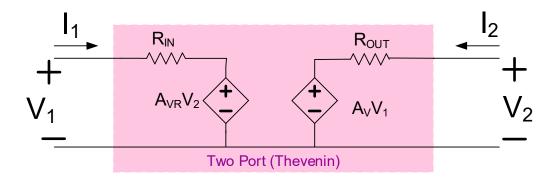

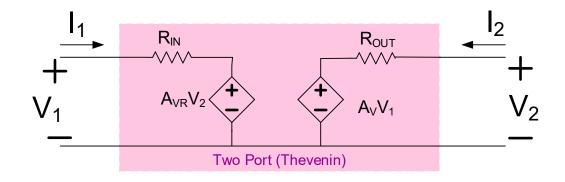

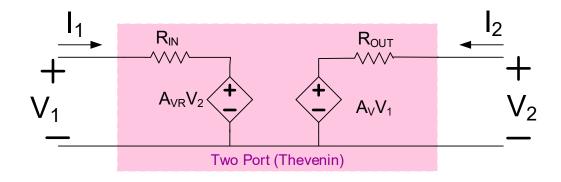

### Two-port representation of amplifiers

- Amplifier often unilateral (signal propagates in only one direction: wlog y<sub>12</sub>=0)

- One terminal is often common

- "Amplifier" parameters often used

- Amplifier parameters can also be used if not unilateral

- One terminal is often common

y parameters

Amplifier parameters

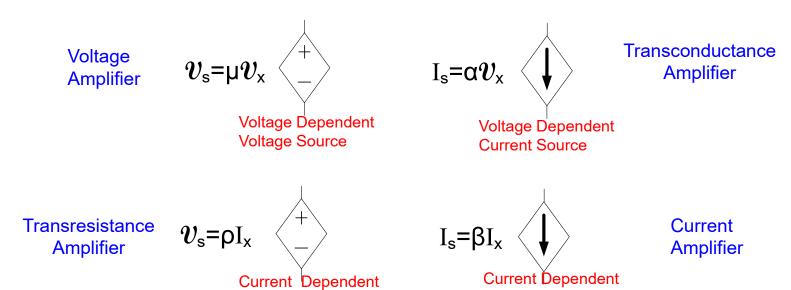

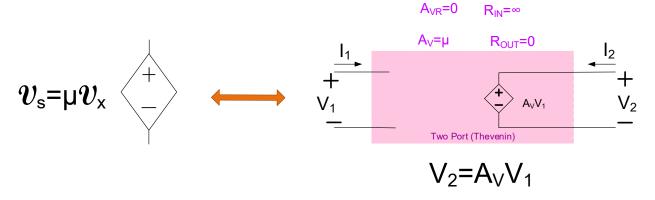

### Relationship with Dependent Sources?

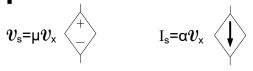

#### Dependent sources from EE 201

Voltage Source

**Current Source**

### Relationship with Dependent Sources?

It follows that

Voltage dependent voltage source is a unilateral floating two-port voltage amplifier with  $R_{IN}=\infty$  and  $R_{OUT}=0$

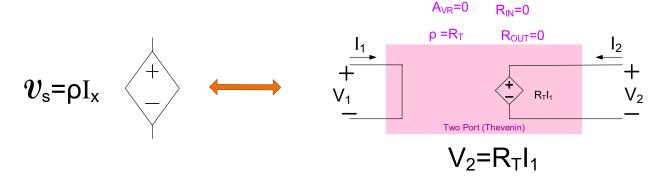

### Relationship with Dependent Sources?

It follows that

Current dependent voltage source is a unilateral floating two-port transresistance amplifier with  $R_{IN}$ =0 and  $R_{OUT}$ =0

Review From Previous Lecture Dependent Sources  $v_s = \mu v_x$   $\downarrow I_s = \alpha v_x$

$$v_s = \rho I_x$$

$\downarrow$

Dependent sources are unilateral two-port amplifiers with ideal input and output impedances

Dependent sources do not exist as basic circuit elements but amplifiers can be designed to perform approximately like a dependent source

- Practical dependent sources typically are not floating on input or output

- One terminal is usually grounded

- Input and output impedances of realistic structures are usually not ideal

Why were "dependent sources" introduced as basic circuit elements instead of two-port amplifiers in the basic circuits courses???

Why was the concept of "dependent sources" not discussed in the basic electronics courses???

### **Topical Coverage Change**

Will have several additional lectures on amplifier structures but will temporarily suspend discussion of amplifiers to consider Thyristors

This is being done to get ready for the Thyristor laboratory experiments

### **Outline**

### Bipolar Processes

- Parasitic Devices in CMOS Processes

- JFET

- Other Junction Devices

### Special Bipolar Processes

ThyristorsSCRTRIAC

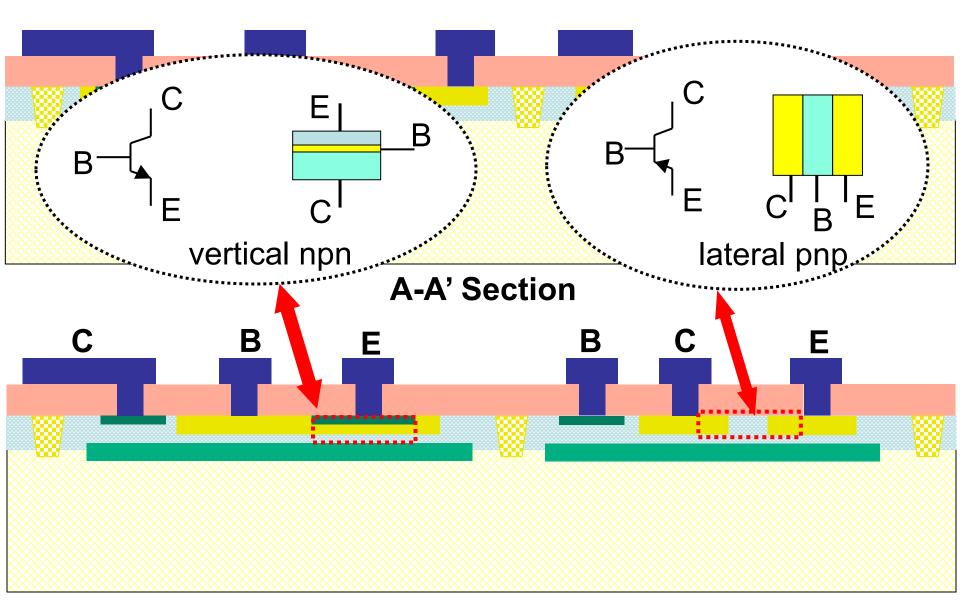

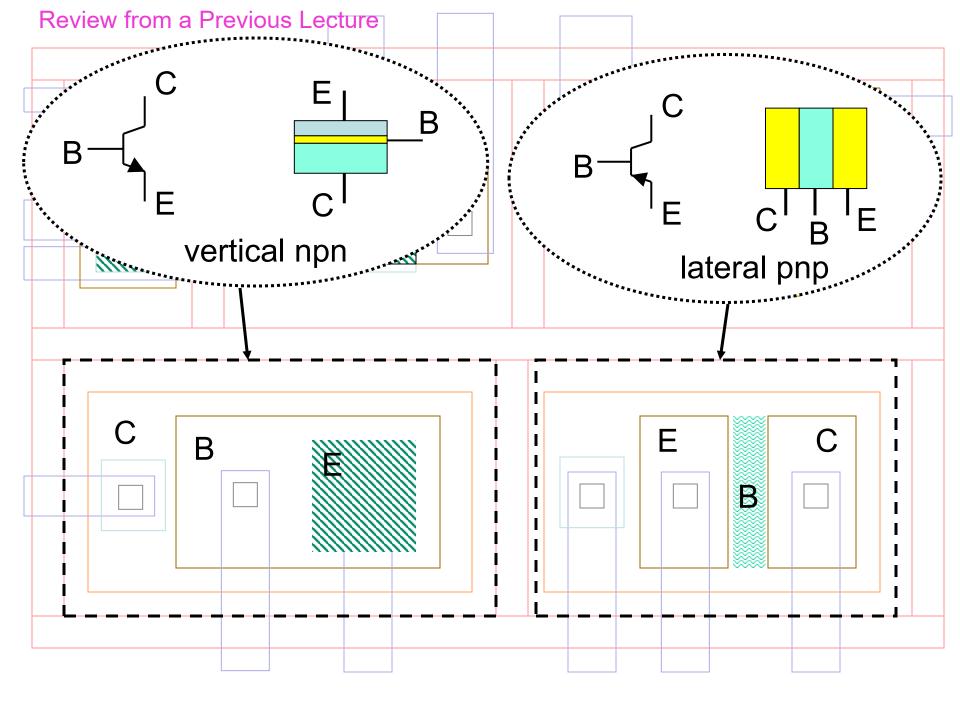

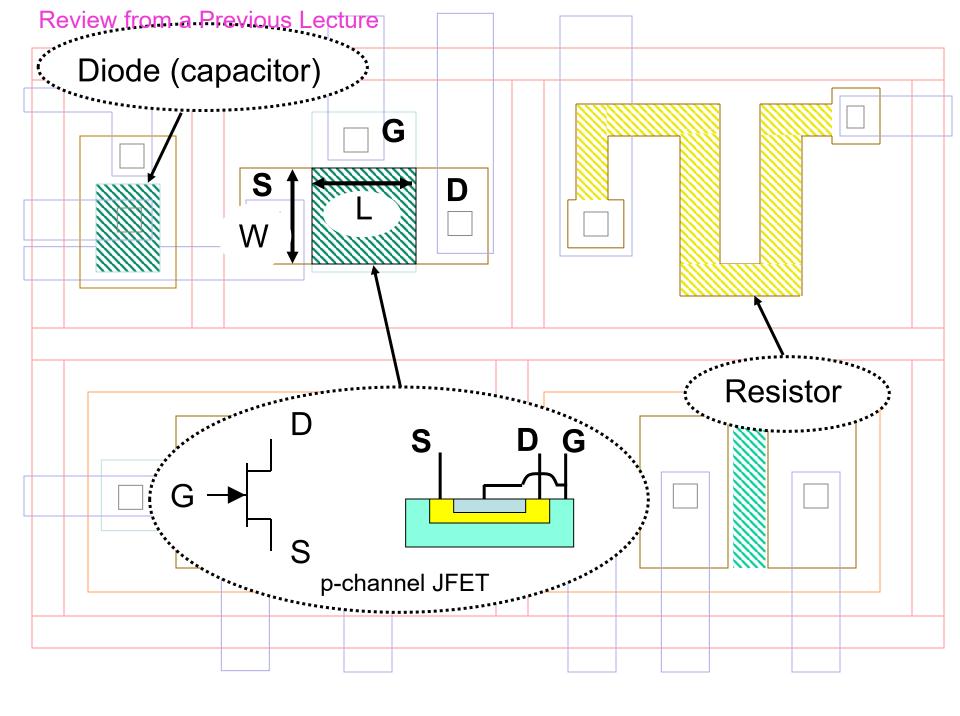

#### Review from a Previous Lecture

**B-B' Section**

#### Review from a Previous Lecture

**B-B' Section**

# Will consider next the JFET but first some additional information about MOS Devices

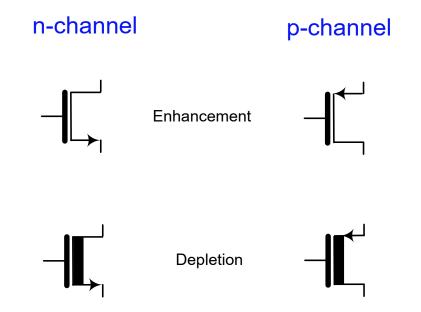

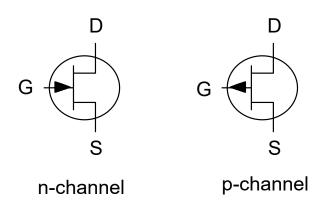

### **Enhancement and Depletion MOS Devices**

- Enhancement Mode n-channel devices

V<sub>⊤</sub> > 0

- Enhancement Mode p-channel devices

V<sub>⊤</sub> < 0</li>

- Depletion Mode n-channel devices

V<sub>T</sub> < 0</li>

- Depletion Mode p-channel devices

V<sub>⊤</sub> > 0

### **Enhancement and Depletion MOS Devices**

- Depletion mode devices require only one additional mask step

- Older n-mos and p-mos processes usually had a depletion device and an enhancement device

- Depletion devices usually not available in CMOS because applications usually do not justify the small increased costs of processing

- The threshold voltage of either n-channel or p-channel devices is adjusted to a desired value by doing a channel implant before gate oxide is applied

### **Outline**

### Bipolar Processes

Parasitic Devices in CMOS Processes

**JFET**

Other Junction Devices

### Special Bipolar Processes

ThyristorsSCRTRIAC

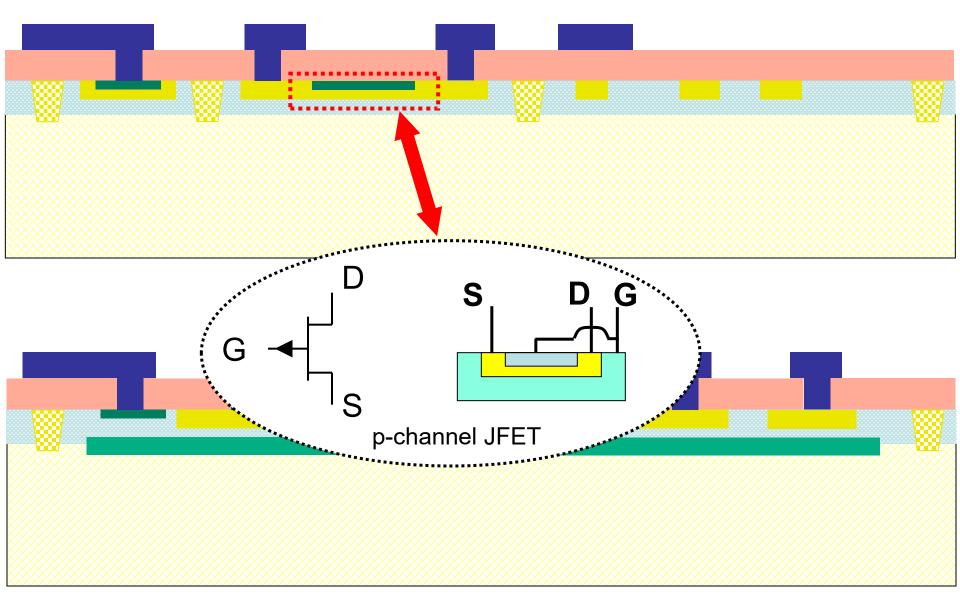

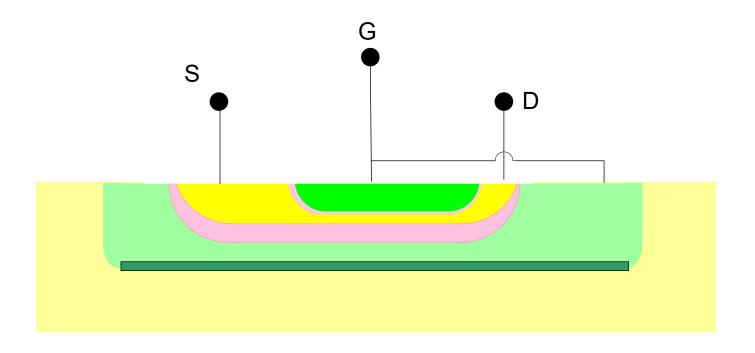

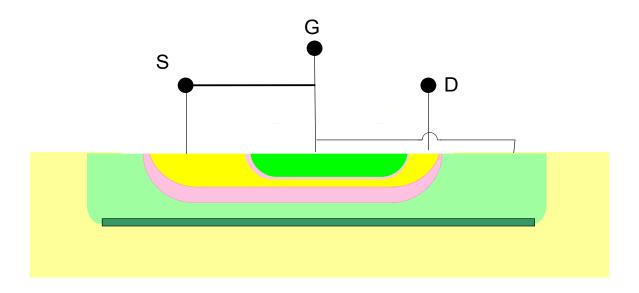

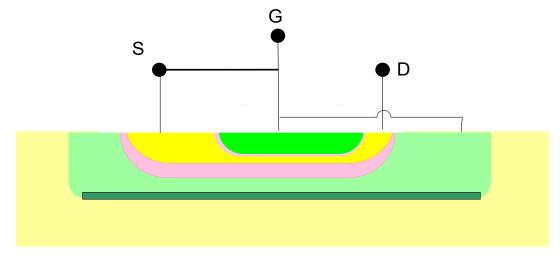

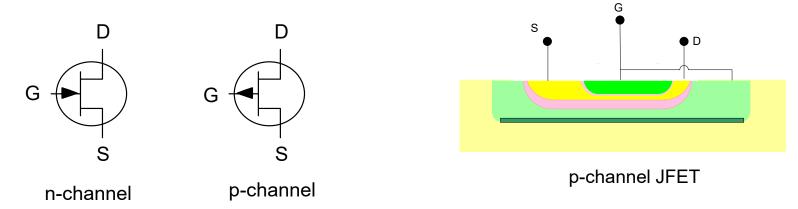

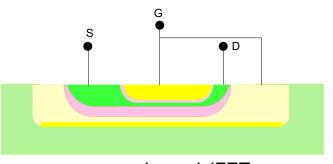

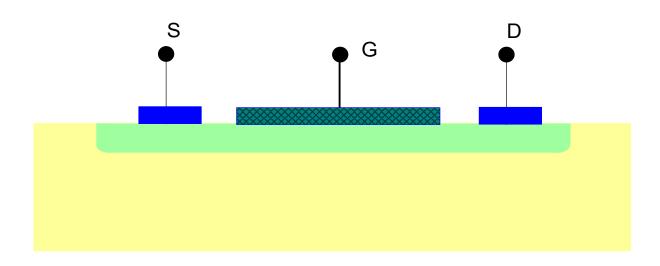

(Parasitic p-channel device in basic bipolar process)

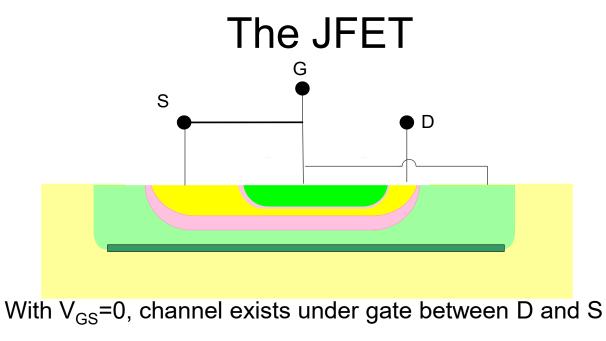

- · Gate is both above and below channel

- With no bias, channel exists between D and S

With  $V_{GS}$ =0, channel exists under gate between D and S

With  $V_{GS}$ =0, channel exists under gate between D and S

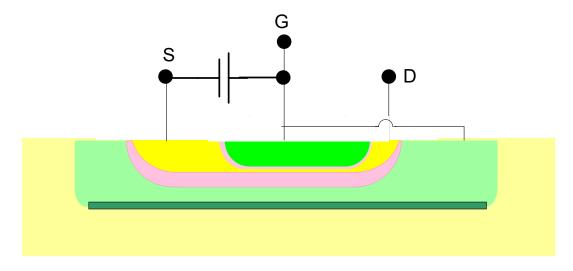

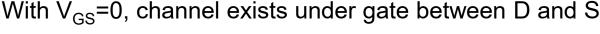

Under small reverse bias (depletion region widens and channel thins)

With  $V_{GS}$ =0, channel exists under gate between D and S

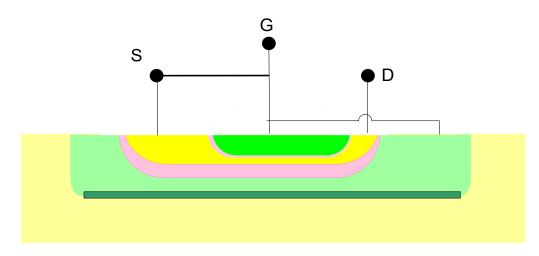

Under sufficiently large reverse bias (depletion region widens and channel disappears - "pinches off")

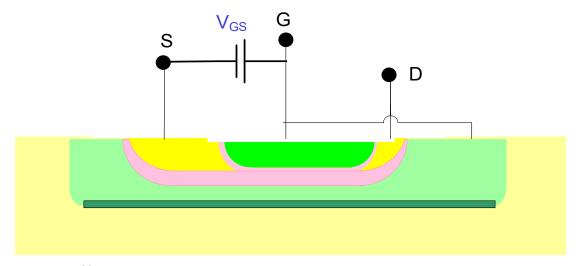

Under small reverse bias and large negative V<sub>DS</sub> (channel pinches off)

#### Square-law model of p-channel JFET

$$\begin{split} I_{D} = & \begin{cases} 0 & V_{GS} > V_{P} \\ \frac{2I_{DSSp}}{V_{P}^{2}} \bigg( V_{GS} - V_{P} - \frac{V_{DS}}{2} \bigg) V_{DS} & -0.3 < V_{GS} < V_{P} & V_{GS} + 0.3 > V_{DS} > V_{GS} - V_{P} \\ I_{DSSp} \bigg( 1 - \frac{V_{GS}}{V_{P}} \bigg)^{2} & -0.3 < V_{GS} < V_{P} & V_{DS} < V_{GS} - V_{P} \end{cases} \end{split}$$

(I<sub>DSSp</sub> carries negative sign)

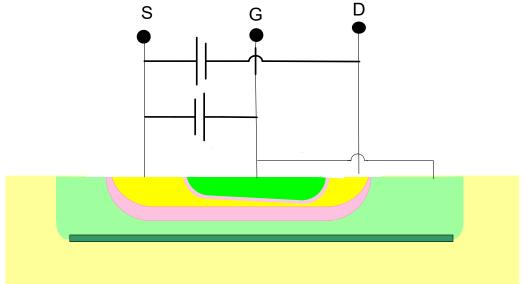

- Functionally identical to the square-law model of MOSFET

- JFET is a depletion mode device

- Parameters I<sub>DSS</sub> and V<sub>P</sub> characterize the device

- I<sub>DSS</sub> proportional to W/L where W and L are width and length of n+ diff

- V<sub>P</sub> is negative for n-channel device, positive for p-channel device thus JFET is depletion mode device

- Must not forward bias GS junction by over about 300mV or excessive base current will flow (red constraint)

- Widely used as input stage for bipolar op amps

n-channel JFET (not available in this process)

#### Square-law model of n-channel JFET

$$I_{D} = \begin{cases} 0 & V_{GS} < V_{P} \\ \frac{2I_{DSS}}{V_{P}^{2}} \left(V_{GS} - V_{P} - \frac{V_{DS}}{2}\right) V_{DS} & 0.3 > V_{GS} > V_{P} & V_{GS} - 0.3 < V_{DS} < V_{GS} - V_{P} \\ I_{DSS} \left(1 - \frac{V_{GS}}{V_{P}}\right)^{2} & 0.3 > V_{GS} > V_{P} & V_{DS} > V_{GS} - V_{P} \end{cases}$$

- Functionally identical to the square-law model of MOSFET

- JFET is a depletion mode device

- Parameters I<sub>DSS</sub> and V<sub>P</sub> characterize the device

- I<sub>DSS</sub> proportional to W/L where W and L are width and length of n+ diff

- V<sub>P</sub> is negative for n-channel device, positive for p-channel device thus JFET is depletion mode device

- Must not forward bias GS junction by over about 300mV or excessive base current will flow (red constraint)

- Widely used as input stage for bipolar op amps

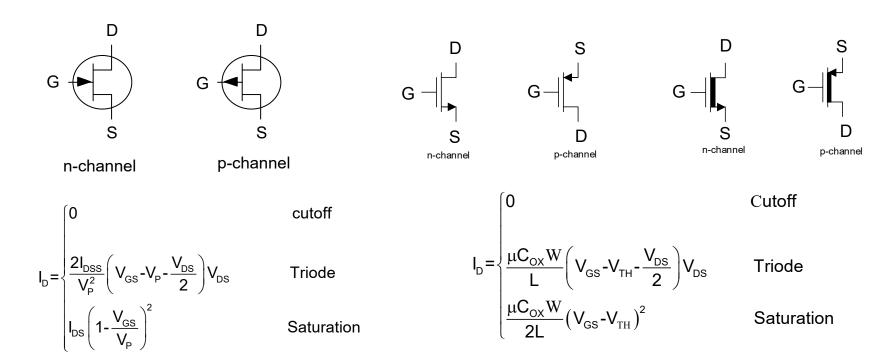

### The FET Devices

$I_{DSS}$  proportional to W/L where W and L are width and length of n+ diff (could define  $I_{DSS} = \hat{I}_{DSS} = \hat{I}_{D$

V<sub>P</sub> and V<sub>TH</sub> are analogous

$$\frac{2\hat{I}_{DSS}}{V_{P}^{2}}$$

and  $\mu C_{OX}$  are analogous

Basic circuit structures are the same (with different biasing implications)

### **Outline**

### **Bipolar Processes**

- Parasitic Devices in CMOS Processes

- JFET

Other Junction Devices

### Special Bipolar Processes

ThyristorsSCRTRIAC

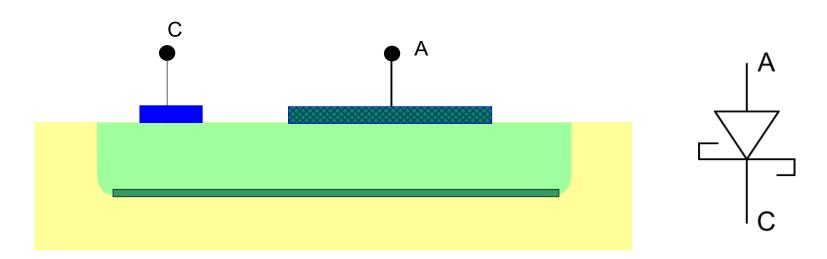

### The Schottky Diode

- Metal-Semiconductor Junction

- One contact is ohmic, other is rectifying

- Not available in all processes

- Relatively inexpensive adder in some processes

- Lower cut-in voltage than pn junction diode

- High speed

### The MESFET

- Metal-Semiconductor Junction for Gate

- Drain and Source contacts ohmic, other is rectifying

- Usually not available in standard CMOS processes

- Must not forward bias very much

- Lower cut-in voltage than pn junction diode

- High speed

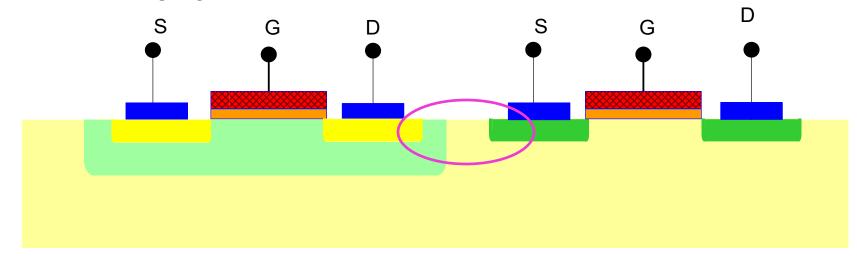

### The Thyristor

A bipolar device in CMOS Processes

#### Consider a Bulk-CMOS Process

Have formed a lateral pnpn device!

Will spend some time studying pnpn devices

### **Outline**

### **Bipolar Processes**

- Parasitic Devices in CMOS Processes

- JFET

- Other Junction Devices

### Special Bipolar Processes

# **Thyristors**

The good and the bad!

## **Thyristors**

The good

**SCRs**

**Triacs**

The bad

Parasitic Device that can destroy integrated circuits

### **Outline**

### **Bipolar Processes**

- Parasitic Devices in CMOS Processes

- JFET

- Other Junction Devices

### Special Bipolar Processes

Thyristors

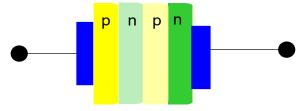

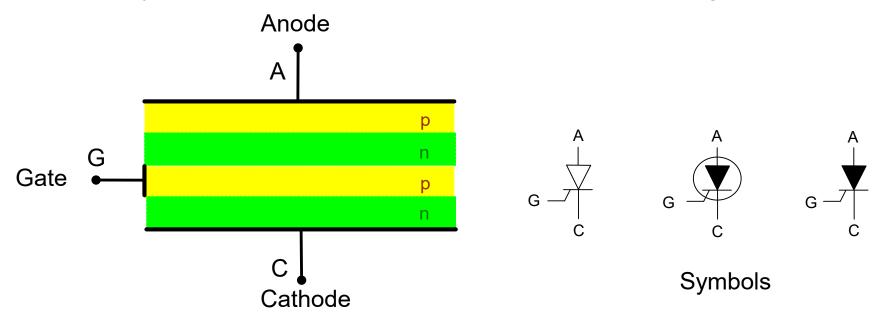

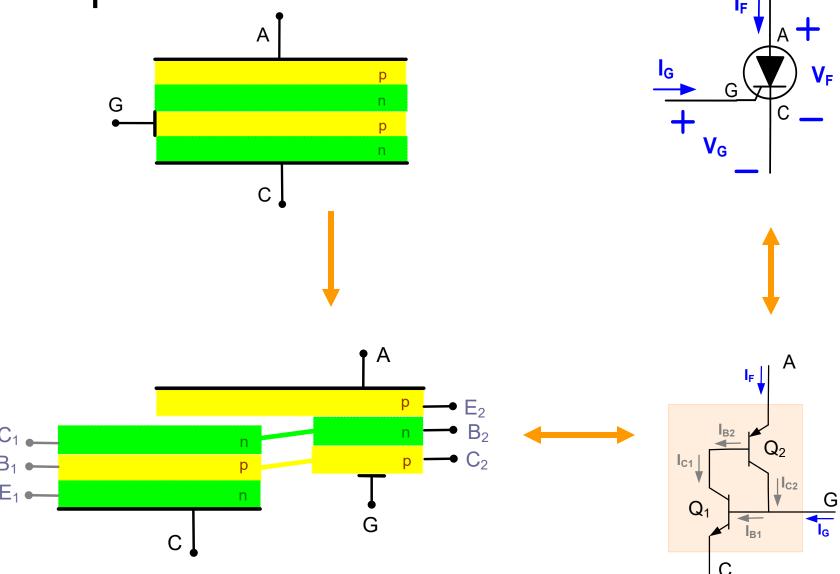

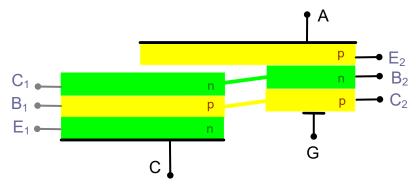

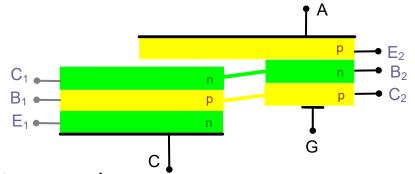

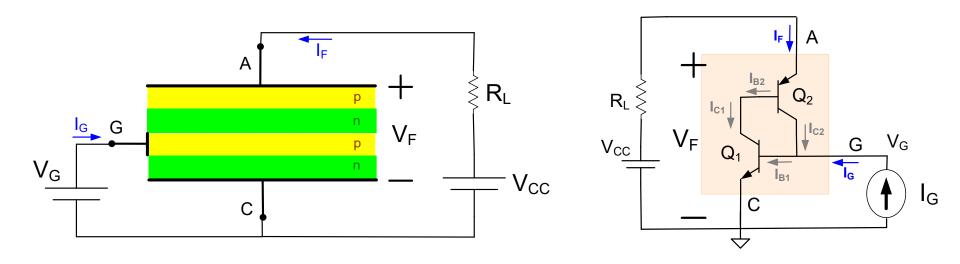

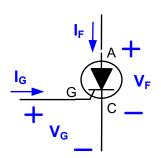

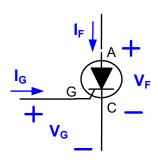

### The SCR

#### Silicon Controlled Rectifier

- Widely used to switch large resistive or inductive loads

- Widely used in the power electronics field

- Widely used in consumer electronic to interface between logic and power

Usually made by diffusions in silicon

Consider first how this 4-layer 3-junction device operates

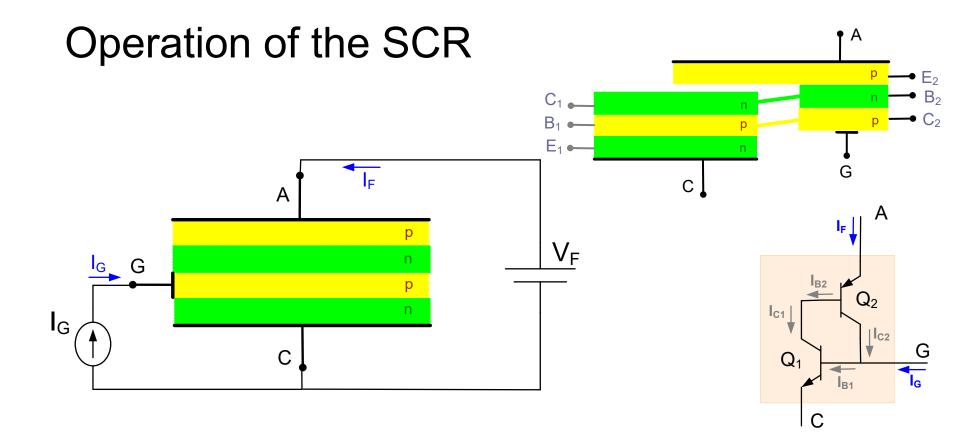

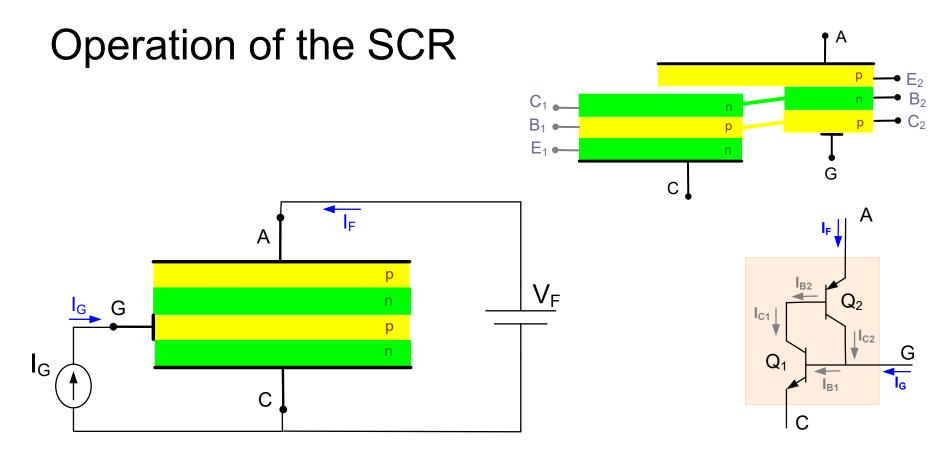

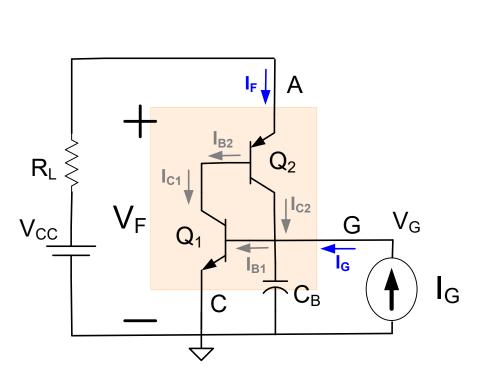

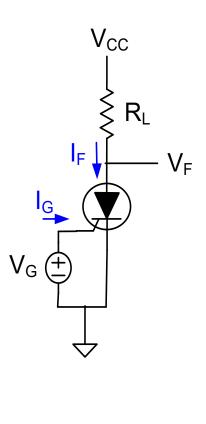

### Operation of the SCR

Not actually separated but useful for describing operation

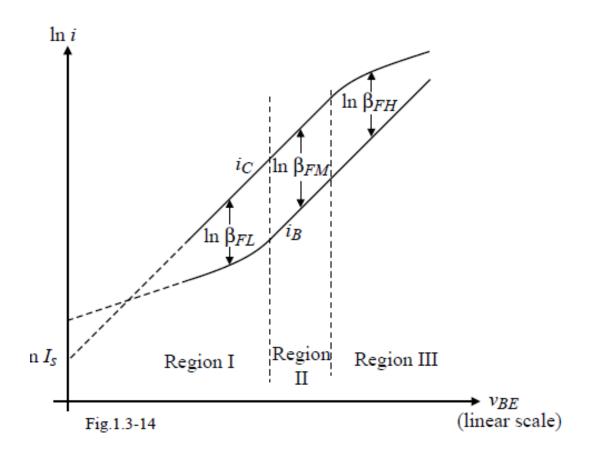

### Variation of Current Gain (β) with Bias for BJT

Note that current gain gets very small at low base current levels

Consider a small positive bias (voltage or current) on the gate (V $_{\rm GC}$  < 0.5V) and a positive and large voltage  $V_{\rm F}$

Will have  $V_{C1} \ge V_F - 0.5V$

Thus Q<sub>1</sub> has a large positive voltage on its collector

Since  $V_{BE1}$  is small,  $I_{C1}$  will be small as will  $I_{C2}$ , diode equation governs BE junction of  $Q_1$   $I_F$  will be very small

Now let bias on the gate increase ( $V_{GC}$  around 0.6V) so  $Q_1$  and  $Q_2$  in FA  $V_{C1} \ge V_F$  - 0.5V

From diode equation, base voltage  $V_{BE1}$  will increase and collector current  $I_{C1}$  will increase Thus base current  $I_{B2}$  will increase as will the collector current of  $I_{C2}$

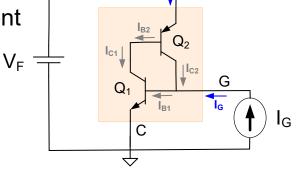

Under assumption of operation in FA region get expression

$$I_{B1} = I_{G} + \beta_1 \beta_2 I_{B1}$$

This is regenerative feedback (actually can show pole in RHP)

### Very Approximate Analysis Showing RHP Pole

$$V_G S C_B + I_{B1} = I_{C2} + I_G$$

$$I_{C2} = \beta_1 \beta_2 I_{B1}$$

$$I_{B1} R_{BE} = V_G$$

$$V_G = I_G \frac{R_{BE}}{sR_{BE}C_B + 1 - \beta_1\beta_2}$$

$$p = \frac{\beta_1 \beta_2 - 1}{R_{BE} C_B}$$

$$V_{C1} \cong V_F - 0.6V$$

Under assumption of operation in FA region get expression

$$I_{B1} = I_G + \beta_1 \beta_2 I_{B1}$$

What will happen with this is regenerative feedback?

If  $I_G$  is small (and thus  $\beta_1$  and  $\beta_2$  are small)  $I_F$  will be very small

If  $I_G$  larger (and  $\beta_1\beta_2I_{B1}>I_G$ ),  $I_G$  can be removed and current will continue to flow

I<sub>C1</sub> will continue to increase and drive Q<sub>1</sub> into SAT

This will try to drive  $V_A$  towards 0.9V (but forced to be  $V_F$ !)

The current in V<sub>F</sub> will go towards ∞

The SCR will self-destruct because of excessive heating!

Too bad the circuit self-destructed because the small gate current was able to control a lot of current!

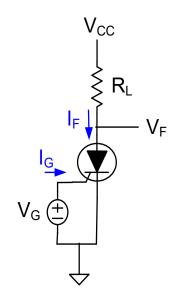

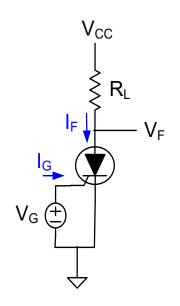

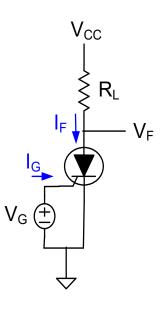

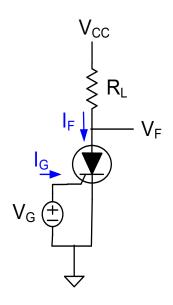

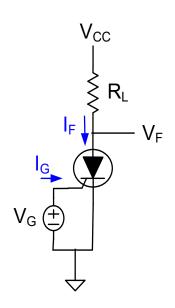

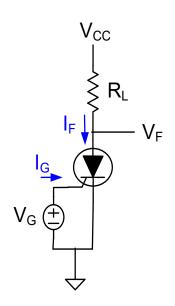

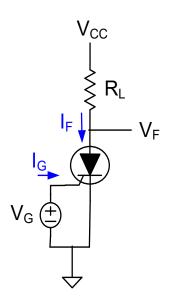

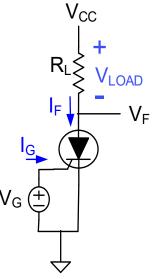

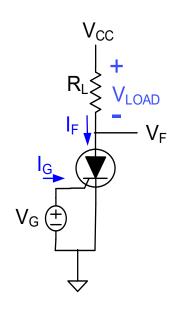

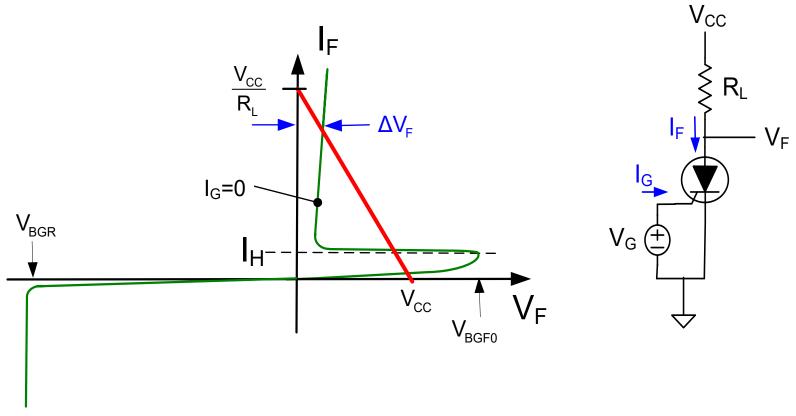

Consider a modified application by adding a load (depicted as R<sub>I</sub>)

All operation is as before, but now, after the triggering occurs, the voltage  $V_F$  will drop to approximately 0.8 V and the voltage  $V_{CC}$ -.8 will appear across  $R_L$

If  $V_{CC}$  is very large, the SCR has effectively served as a switch putting  $V_{CC}$  across the load and after triggering occurs,  $I_{C}$  can be removed!

But, how can we turn it off?

Will discuss that later

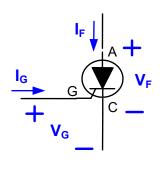

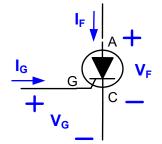

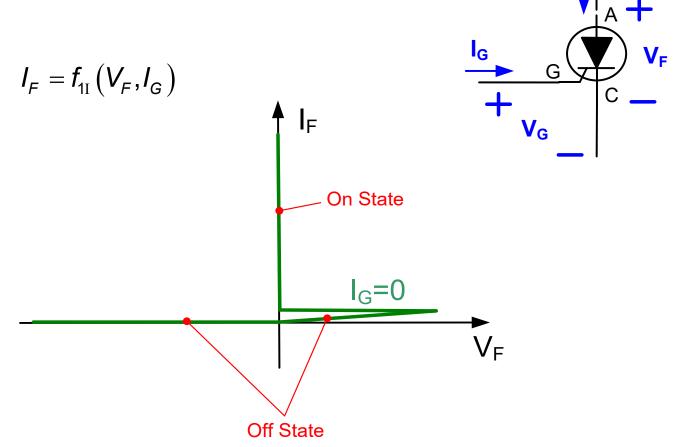

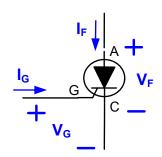

SCR model

$$I_{F} = f_{1}(V_{F}, V_{G})$$

$$I_{G} = f_{2}(V_{G})$$

As for MOSFET, Diode, and BJT, several models for SCR can be developed

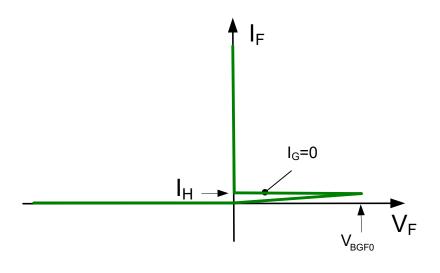

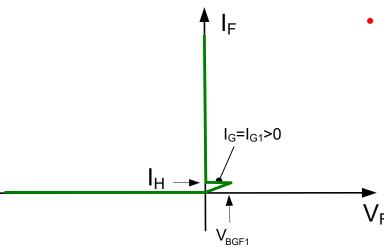

The Ideal SCR Model

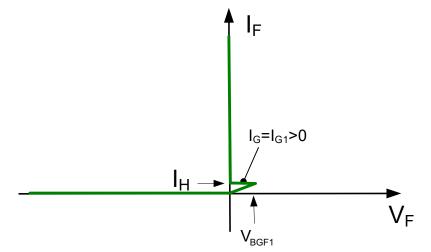

$$I_{F} = f_{1I}(V_{F}, I_{G})$$

$$I_{G} = f_{2I}(V_{G})$$

or

$$I_{F} = f_{1IA} (V_{F}, V_{G})$$

$$I_{G} = f_{2I} (V_{G})$$

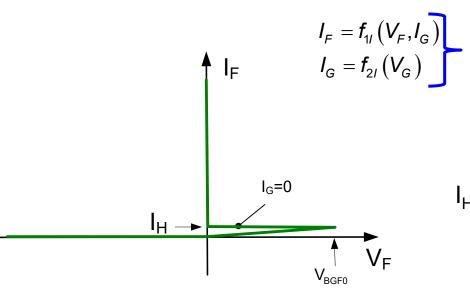

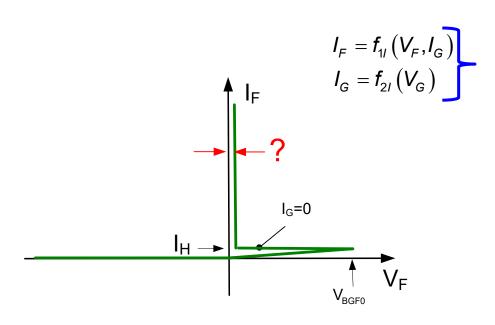

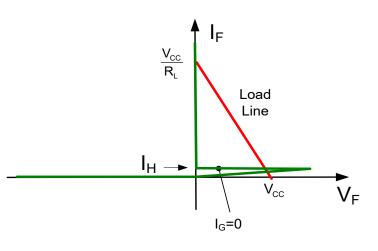

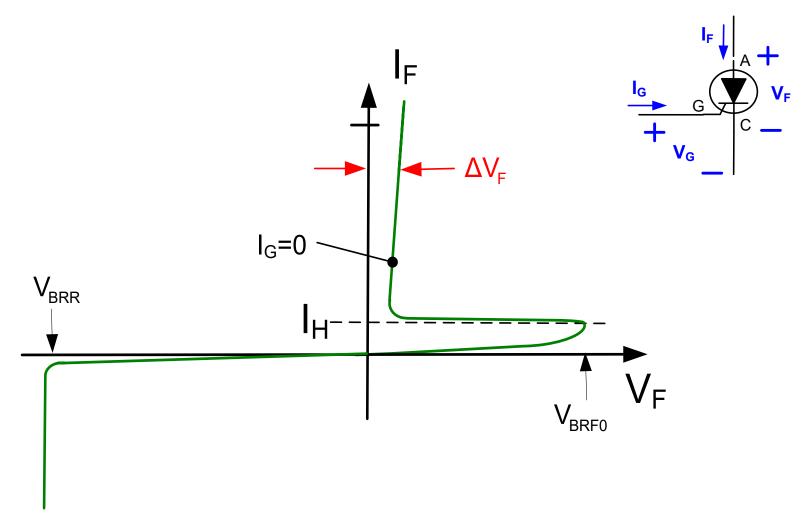

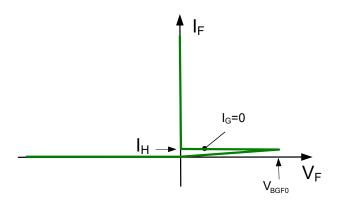

Consider the Ideal SCR Model

I<sub>H</sub> is very small

I<sub>G1</sub> is small (but not too small)

Consider nearly Ideal SCR Model

- On voltage approximately 0.9V

- Major contributor to ON-state power dissipation

- Even with large currents, P<sub>ON</sub> is quite small

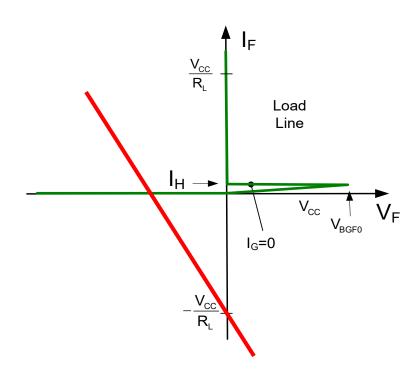

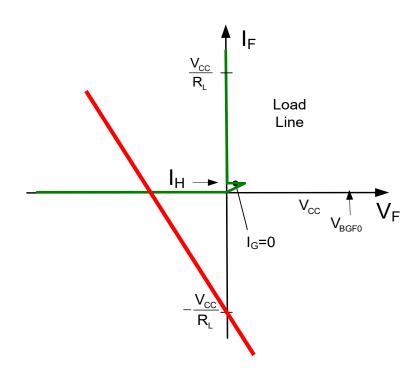

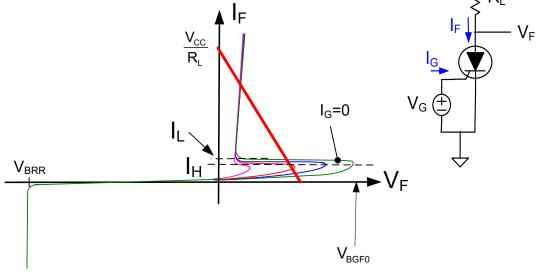

#### **Operation with the Ideal SCR**

$$I_F = f_1(V_F, V_G)$$

$$I_G = f_2(V_G)$$

$$V_{CC} = I_F R_L + V_F$$

$$V_{CC} = I_F R_L + V_F$$

$$I_F = f_{1I} (V_F, V_G)$$

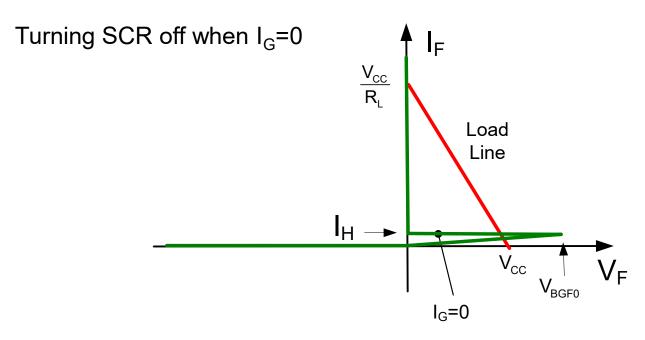

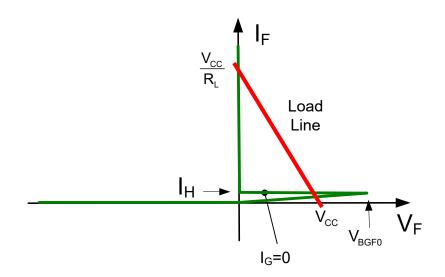

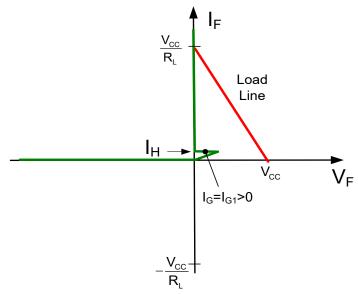

The solution of these two equations is at the intersection of the load line and the device characteristics

when I<sub>G</sub>=0

Note three intersection points Two (upper and lower) are stable equilibrium points, one is not

When operating at upper point,  $V_F=0$  so  $V_{CC}$  appears across  $R_L$  We say SCR is ON

When operating at lower point,  $I_F$  approx 0 so no signal across  $R_L$  We say SCR is OFF

When I<sub>G</sub>=0, will stay in whatever state it was in

### **Operation with the Ideal SCR**

For notational convenience will drop subscript unless emphasis is needed

#### Operation with the Ideal SCR

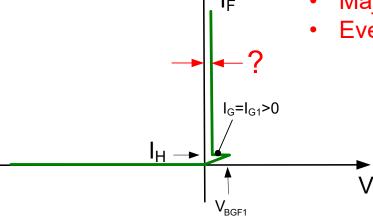

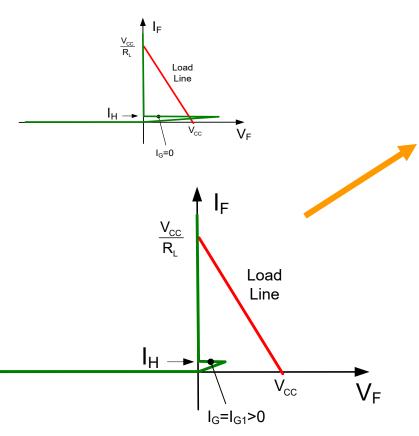

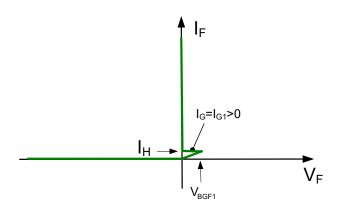

Now assume it was initially in the OFF state and then a gate current was applied

$$V_{CC} = I_F R_L + V_F$$

$$I_F = f (V_F, I_G)$$

Now there is a single intersection point so a unique solution

The SCR is now ON

Removing the gate current will return to the previous solution (which has 3 intersection points) but it will remain in the ON state

#### **Operation with the Ideal SCR**

Reduce  $V_{CC}$  so that  $V_{CC}/R_L$  goes below  $I_H$

This will provide a single intersection point

V<sub>CC</sub> can then be increased again and SCR will stay off

Must not increase  $V_{CC}$  much above  $V_{BGF0}$  else will turn on

### **Operation with the Ideal SCR**

Turning SCR off when I<sub>G</sub>=0

### Operation with the Ideal SCR

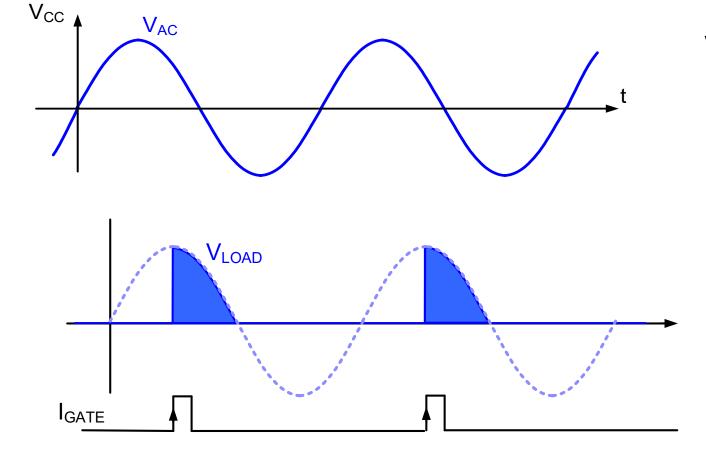

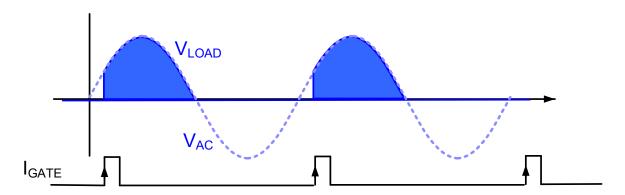

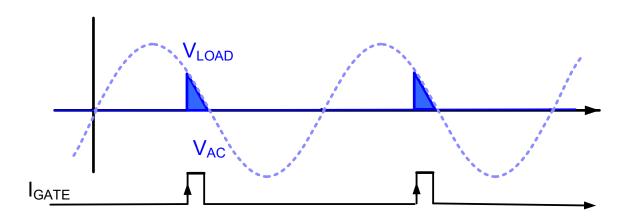

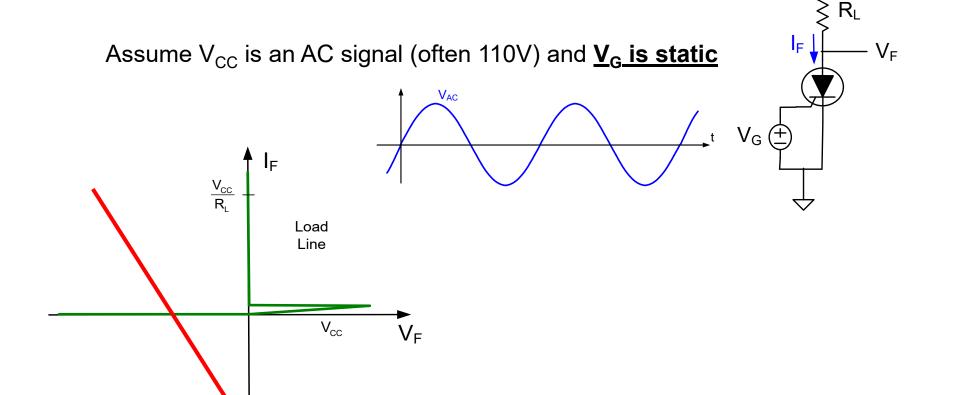

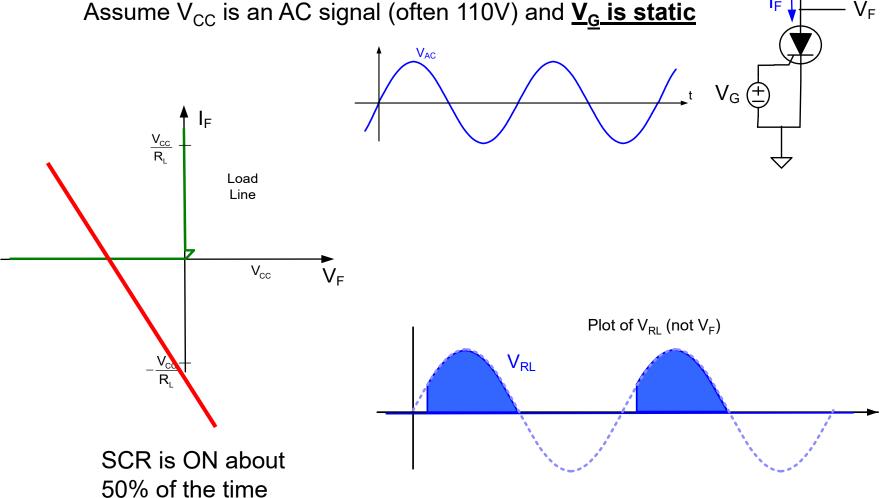

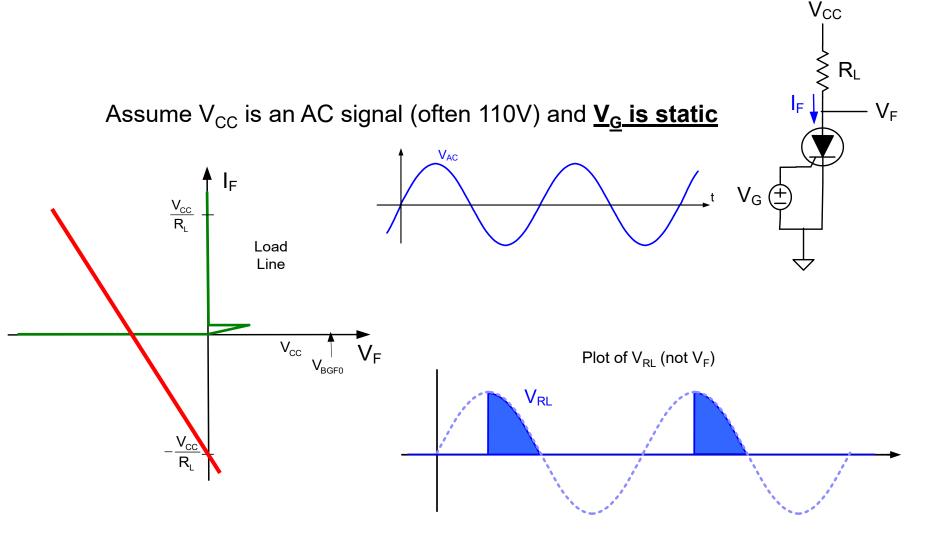

Often V<sub>CC</sub> is an AC signal (often 110V)

SCR will turn off whenever AC signal goes negative

#### Operation with the Ideal SCR

Often V<sub>CC</sub> is an AC signal (often 110V)

SCR will turn off whenever AC signal goes negative

#### Operation with the Ideal SCR

Turning SCR off when I<sub>G</sub>>0

This will provide a single intersection point

But when V<sub>CC</sub> is then increased SCR will again turn on

### **Operation with the Ideal SCR**

Duty cycle control of load R<sub>L</sub>

### **Operation with the Ideal SCR**

Duty cycle control of load R<sub>L</sub>

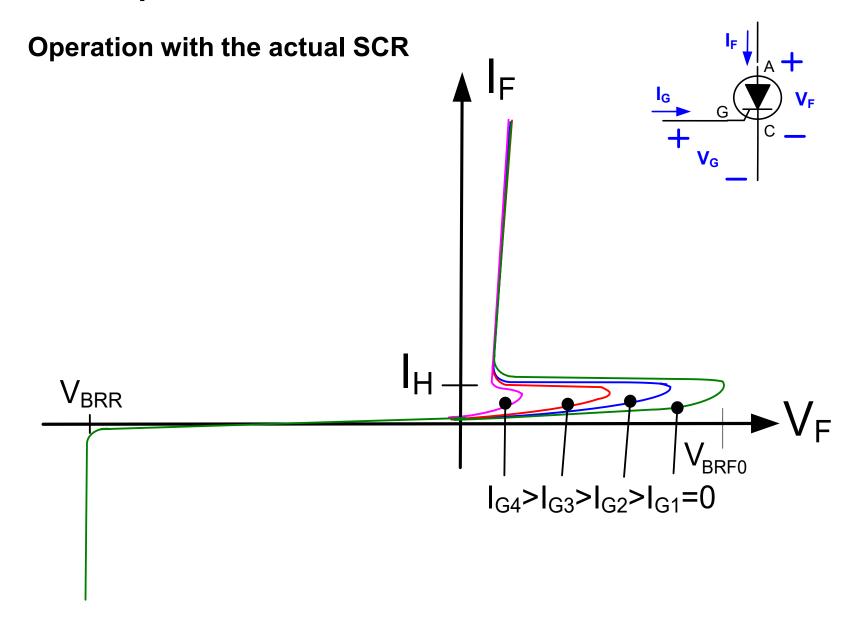

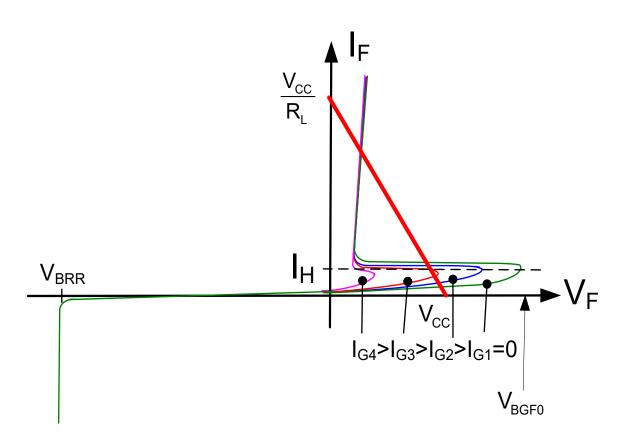

### **Operation with the actual SCR**

#### Operation with the actual SCR

- Still two stable equilibrium points and one unstable point

- $\Delta V_F$  is quite constant and small (around 1V)

- If large current is flowing, power in anode can be large  $(P_A \approx I_F \bullet 1V)$

- Power in gate is usually very small

#### **Operation with the actual SCR**

To turn on, must make I<sub>G</sub> large enough to have single intersection point

#

$V_{BGF0}$

$I_H$  is the holding current  $I_L$  is the latching current (current immediately after turn-on)  $V_{BGF0}$  is the forward break-over voltage  $V_{BRR}$  is the reverse break-down voltage  $I_{GT}$  is the gate trigger current  $V_{GT}$  is the gate trigger voltage

**SCR Terminology**

Issues and Observations

- Trigger parameters (V<sub>GT</sub> and I<sub>GT</sub>) highly temperature dependent

- Want gate "sensitive" but not too sensitive (to avoid undesired triggering)

- SCRs can switch very large currents but power dissipation is large

- Heat sinks widely used to manage power

- Trigger parameters affected by both environment and application

- Trigger parameters generally dependent upon VF

- Exceeding V<sub>BRR</sub> will usually destroy the device

- Exceeding V<sub>BGF0</sub> will destroy some devices

- Lack of electronic turn-off unattractive in some applications

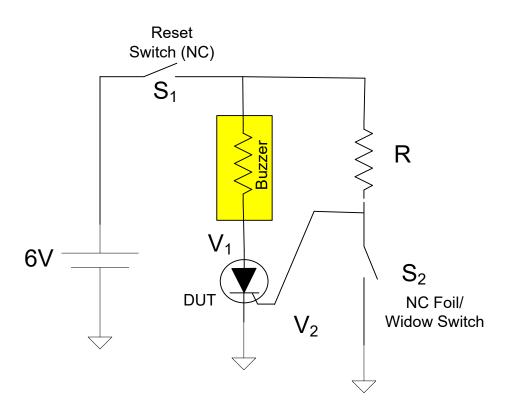

- Can be used in alarm circuits to attain forced reset

- Maximum 50% duty cycle in AC applications is often not attractive

# Alarm Application

### **Performance Limitations with the SCR**

- Very attractive properties as an electronic switch

- SCR is very useful

#### But:

- 1. Only conducts in one direction

- 2. Can't easily turn off (though not major problem in AC switching)

### **Observations about Basic SRC Circuit**

$V_{CC}$

SCR is always off

### **Observations about Basic SRC Circuit**

Assume  $V_{CC}$  is an AC signal (often 110V) and  $\underline{V_G}$  is static

$V_{\text{CC}}$

$R_L$

### **Observations about Basic SRC Circuit**

SCR is ON less than 50% of the time (duty cycle depends upon  $V_G$ )

Often use electronic circuit to generate  $V_G$

### Performance Limitations with the SCR

- · Very attractive properties as an electronic switch

- SCR is very useful

#### But:

- 1. Only conducts in one direction

- 2. Can't easily turn off (though not major problem in AC switching)

Would be useful in many additional applications if:

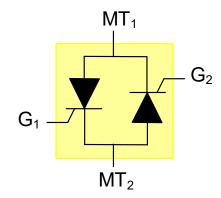

- 1. Could conduct in both directions

- 2. Can easily turn off with I<sub>G</sub>

### Improvement Concept

- 1. Only conducts in one direction

- 2. Can't easily turn off (though not major problem in AC switching)

- 1. Could conduct in both directions

- 2. Generating two gate voltages referenced to different cathodes a bit cumbersome

Will investigate bi-directional devices in next lecture

Stay Safe and Stay Healthy!

## End of Lecture 29